source (input)

drain (output)

gate (signal)

send a small positive charge to gate,

then there is current from source to drain,

and the drain pin output = 1 ,

otherwise send a small negative charge, then = 0

ISA instruction set architecture

instructions, data type, registers

hardware support for managing in machine language

APU AMD = accelerated processing unit = CPU+GPU(graphic p.u.) both in one DIE

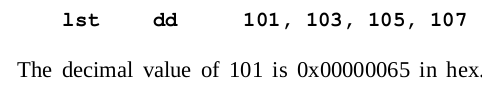

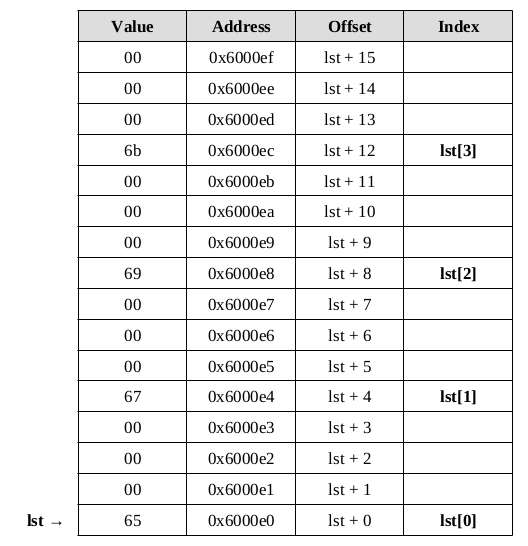

Hex digit = Nibble

0x0 = 0000

0x1 = 0001

0x2 = 0010

0x3 = 0011

0x4 = 0100

0x5 = 0101

0x6 = 0110

0x7 = 0111

0x8 = 1000

0x9 = 1001

0xa = 1010

0xb = 1011

0xc = 1100

0xd = 1101

0xe = 1110

0xf = 1111

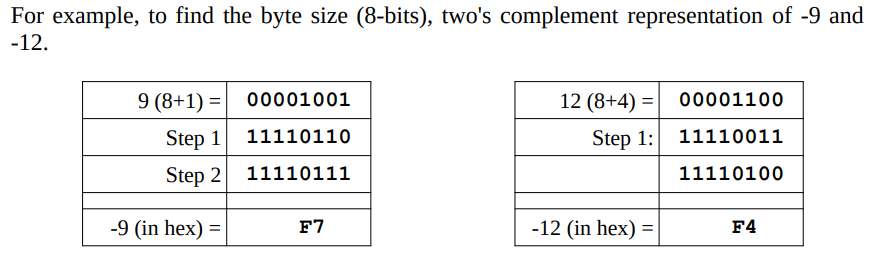

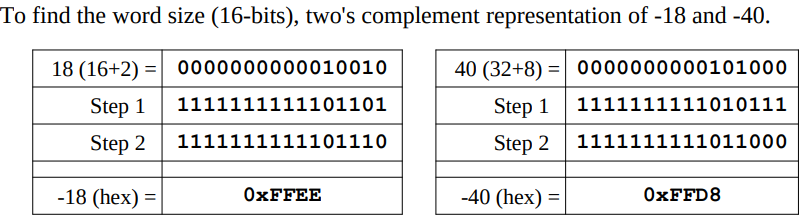

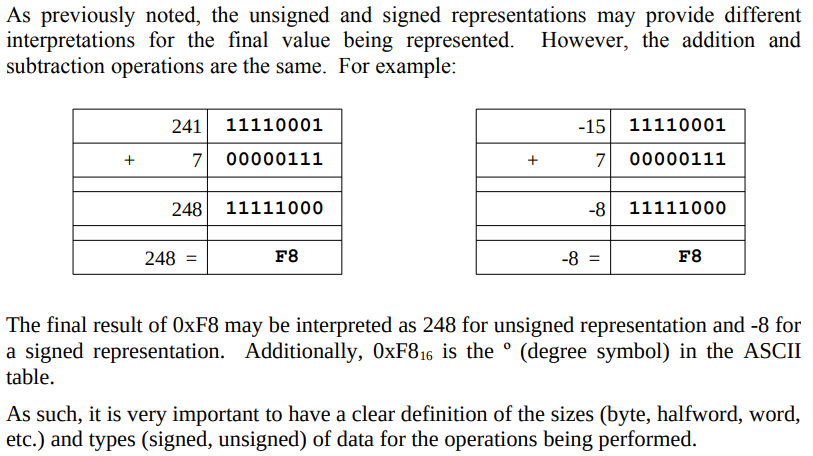

1 = 00000001 = 0x01

-1 = 11111110+1 = 11111111 = 0xFF

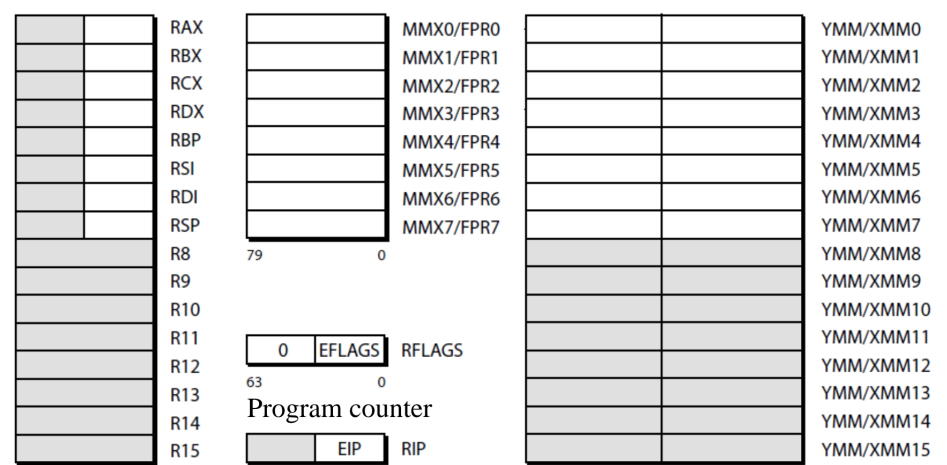

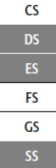

Segment registers (16 bit not available with 8 bit)

CS Code S

DS Data S

SS Stack S

ES Extra S

FS

GS

MMX 8 registers 64 bit

XMMn 16 registers 128 bit

YMMn 16 registers 256 bit

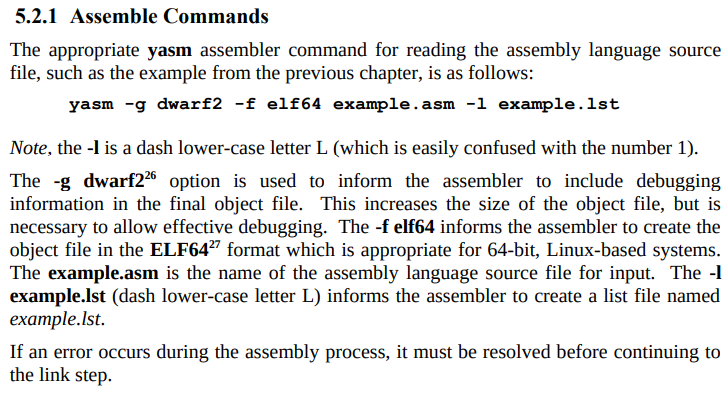

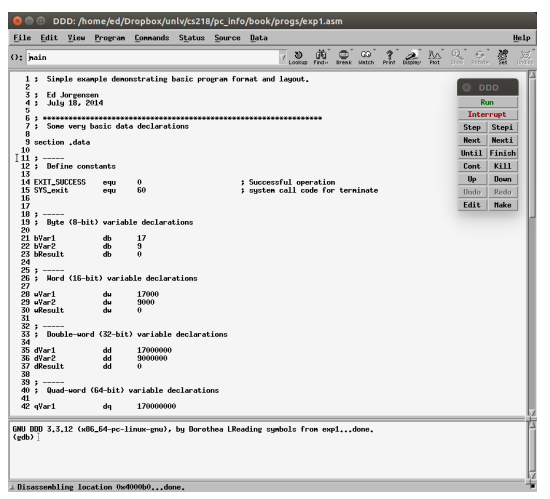

yasm -g dwarf2 -f elf64 prog.asm -l progr.lst

ld -g -o prg prog.o

./

ddd prg

the option -c is used to create an object file

example:

gcc -Wall -c prog.c // creates prog.o

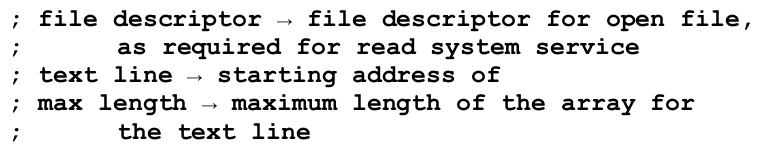

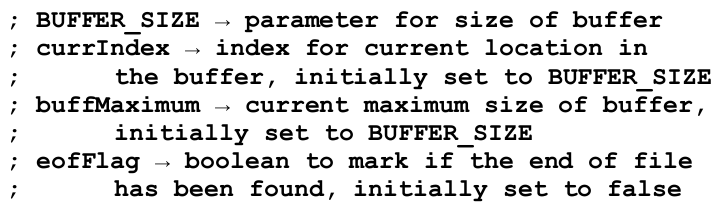

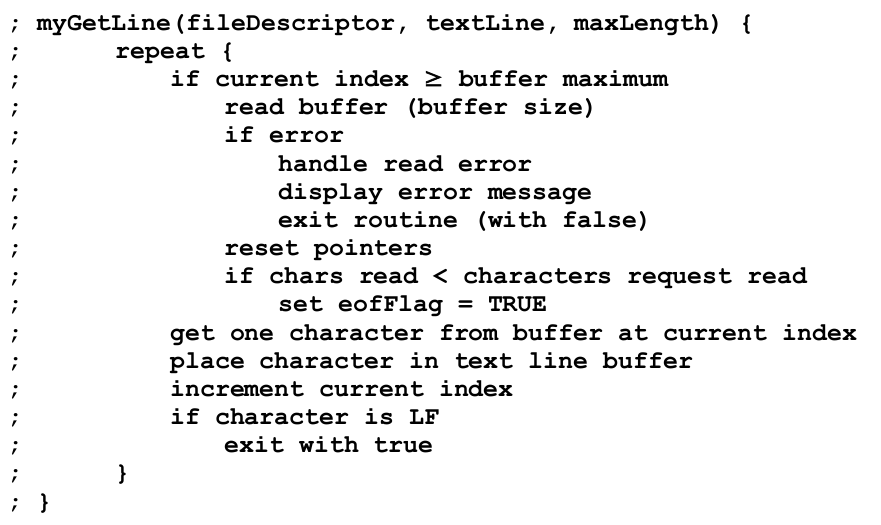

BUFFERING

NO SYS_exit = Segmentatio fault , Core Dump

Operand must be a register

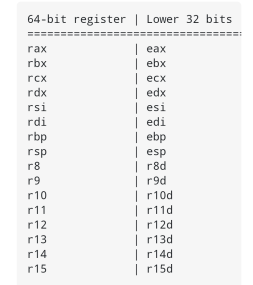

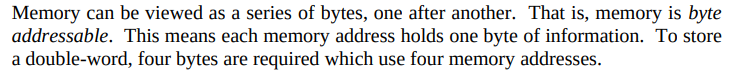

Data must be moved into a CPU register from RAM in order to be operated upon. Once the calculations are completed, the result may be copied from the register and placed into a variable

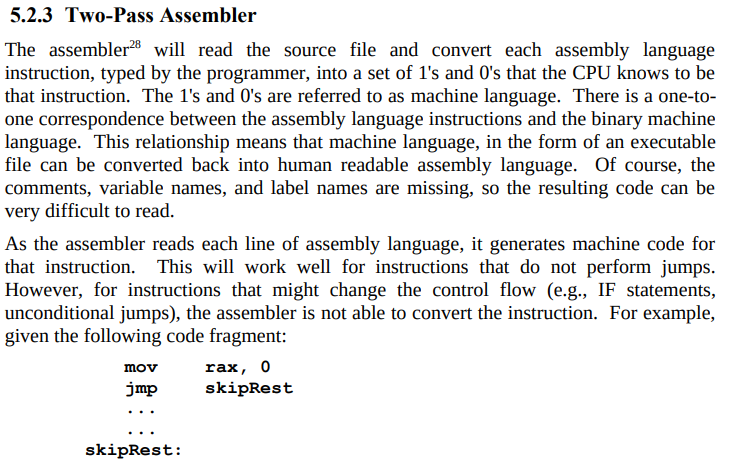

mov dest, src

The source operand is copied from the source operand into the destination operand. The value of the source operand is unchanged. The destination and source operand must be of the same size (both bytes, both words, etc.).

The destination operand cannot be an immediate.

Both operands cannot be memory. If a memory to memory operation is required, two instructions must be used

mov eax, dword [var0]

mov dword [var1], eax

for double-word destination and source operand, the upper-order portion of the quadword register is set to 0.

The only way to access memory is with the brackets [].

Omitting the brackets will not access memory and instead obtain the address of the item. For example:

mov rax, qword [var1] ; value of var1 in rax

mov rax, var1 ; address of var1 in rax

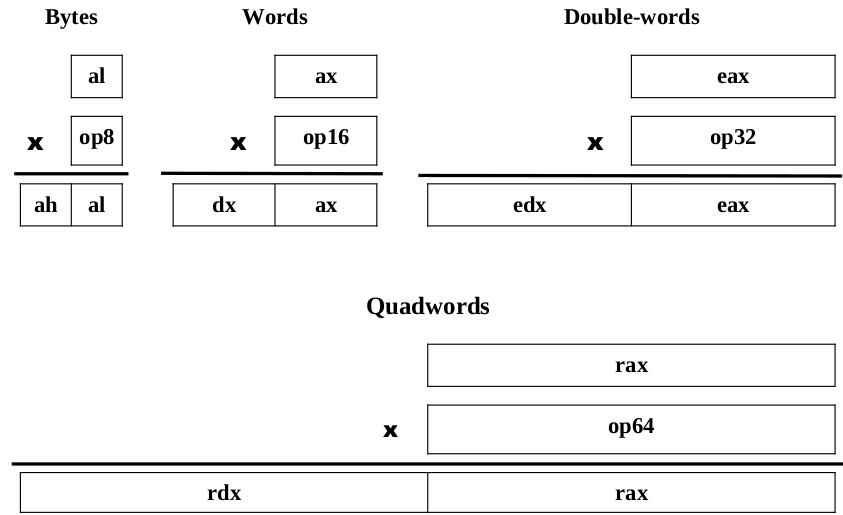

MUL

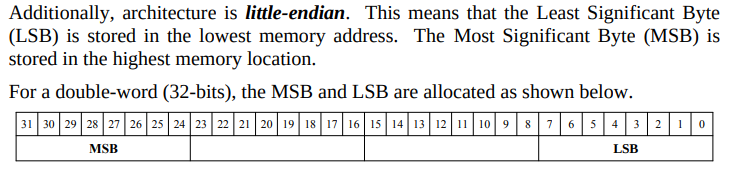

Since the 64-bit architecture only has 64-bit registers, the 128-bit result is, and must be, placed in two different quadword (64-bit) registers,

rdx for the upper-order result and rax for the lower-order result,

which is typically written as rdx:rax (by convention).

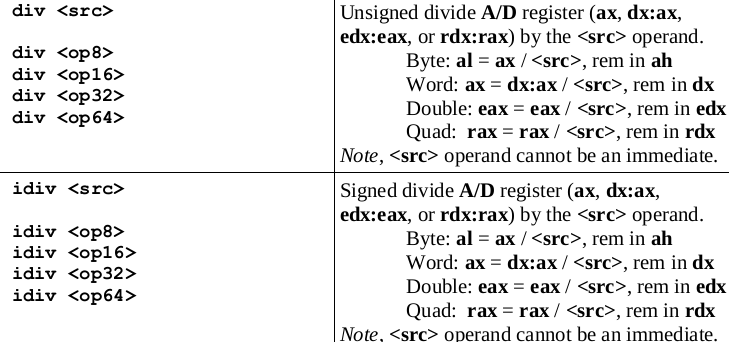

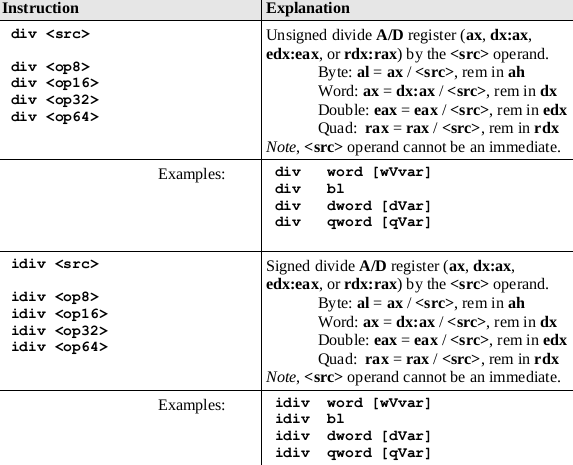

DIV

ADDRESSING